#### RISC-V°

#### Instruction Sets Want to be Free of Gravity!

RISC-V

5 C C C C C

Krste Asanovic Prof. EECS, UC Berkeley; Chairman, RISC-V Foundation; Co-Founder and Chief Architect, SiFive Inc.

IEEE Space Computing Conference August 26, 2021

# Why Instruction Set Architecture matters

#### Why can't Intel sell mobile chips?

- 99%+ of mobile phones/tablets based on ARM v7/v8 ISA

- Why can't ARM partners sell servers?

- 99%+ of servers based on AMD64 ISA (most built by Intel)

- How can IBM still sell mainframes?

- IBM 360, oldest surviving ISA (50+ years)

ISA is most important interface in computer system where software meets hardware

# **Companies and their ISAs Come and Go**

- Digital Equipment Corporation, RIP! (PDP-11, VAX, Alpha)

- Intel's dead ISAs (i960, i860, Itanium, ...)

- SPARC

- Sun opened v8 as IEEE 1754-1994

- Acquired by Oracle, SPARC development closed down in 2017

- MIPS

- Sold to Imagination, bought by Wave

- Opened up MIPS R6 ISA in 2018, then made *not* open in 2019

#### IBM POWER

- Initially proprietary, opened up in 2019 as OpenPower

- ARM

- Sold to Softbank in 2016

- In 2020, Nvidia announced acquiring ARM

# **Open Interfaces Work for Software!**

| Field      | Open Standard    | Free, Open Implement. | Proprietary Implement. |

|------------|------------------|-----------------------|------------------------|

| Networking | Ethernet, TCP/IP | Many                  | Many                   |

| OS         | Posix            | Linux, FreeBSD        | M/S Windows            |

| Compilers  | С                | gcc, LLVM             | Intel icc, ARMcc       |

| Databases  | SQL              | MySQL, PostgresSQL    | Oracle 12C, M/S DB2    |

| Graphics   | OpenGL           | Mesa3D                | M/S DirectX            |

| ISA        | ??????           |                       | x86, ARM, IBM360       |

Why not successful free & open standards and free & open implementations, like other fields?

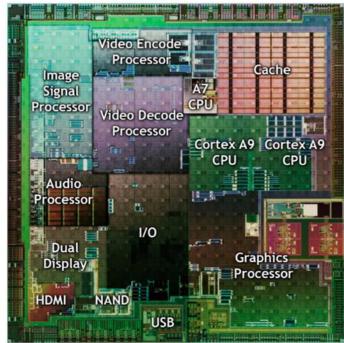

## Today, many ISAs on one SoC

- Applications processor (usually ARM)

- Graphics processors

- Image processors

- Radio DSPs

- Audio DSPs

- Security processors

- Power-management processor

- > dozen ISAs on some SoCs each with unique software stack

#### Why?

- Apps processor ISA too big, inflexible for accelerators

- IP bought from different places, each proprietary ISA

- Engineers build home-grown ISA cores

NVIDIA Tegra SoC

# Do we need all these different ISAs? Must they be proprietary? Must they keep disappearing?

What if there was one stable free and open ISA everyone could use for everything?

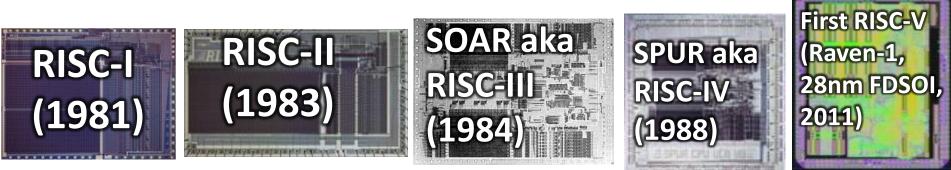

## **RISC-V Background**

- In 2010, after many years and many research projects using MIPS, SPARC, and x86, time for architecture group at UC Berkeley to choose ISA for next set of projects

- Obvious choices: x86 and ARM

- x86 impossible too complex, IP issues

- ARM mostly impossible complex, no 64-bit in 2010, IP issues

- So we started "3-month project" during summer 2010 to develop clean-slate ISA

- Principal designers: Andrew Waterman, Yunsup Lee, David Patterson, Krste Asanovic

- Four years later, May 2014, released frozen base user spec

- many tapeouts and several research publications along the way

- Name RISC-V (pronounced "risk-five") represents fifth major Berkeley RISC ISA

## Hot Chips 2014

₹

2

8

2

## **RISC-V** is not first open ISA

- MIL-STD-1750A

- Previous open military ISA defined by US Air Force, deprecated for new designs in 1996

- SPARC International

- SPARC v8 IEEE standard, used by LEON for European Space Agency

- OpenRISC

- Some uptake but project languishing in 2010, focused on core not ISA

- RISC-V has far broader acceptance and uptake than any of these

#### **RISC-V** International

- **RISC-V** is the opensource hardware Instruction Set Architecture (ISA)

- Frozen base user spec released in 2014, contributed, ratified, and openly published by RISC-V International

**RISC-V International** is a non-profit entity serving members and the industry

Our mission is to accelerate RISC-V adoption with shared benefit to the entire community of stakeholders.

- Drive progression of ratified specs, compliance suite, and other technical deliverables

- Grow the overall ecosystem / membership, promoting diversity while preventing fragmentation

- Deepen community engagement and visibility

#### **Open-source software:** Gcc, binutils, glibc, Linux, BSD, LLVM, QEMU, FreeRTOS,

ZephyrOS, LiteOS, SylixOS, ...

Software

#### **Commercial software:**

Lauterbach, Segger, IAR, Micrium, ExpressLogic, Ashling, Imperas, AntMicro, ...

ISA specification

Golden Model

Compliance

#### Hardware

#### **Open-source cores:**

RISC-

International

Rocket, BOOM, RI5CY, Ariane, PicoRV32, Piccolo, SCR1, Swerv, Hummingbird, WARP-V, XiangShan, ...

#### **Commercial core providers:**

Alibaba, Andes, Bluespec, Cloudbear, Cobham, Codasip, Cortus, InCore, MIPS, Nuclei, Semidynamics, SiFive, StarFive, Syntacore, ... Inhouse cores: Nvidia, WDC, Alibaba, +others

## What's Different about RISC-V?

- Far smaller than other commercial ISAs

- Clean-slate design

- Clear separation between user and privileged ISA

- Avoids µarchitecture or technology-dependent features

- Modular ISA designed for extensibility/specialization

- Small standard base ISA, with multiple standard extensions

- Sparse &variable-length instruction encoding for vast opcode space

- Stable

- Base and first standard extensions are frozen

- Additions via optional extensions, not new versions

- Community designed

- Developed with leading industry/academic experts and software developers

#### Engaged engineers are domain experts Drive technical priorities in 20+ focus areas

Opcode Space Mgmt Standing Committee Software Standing Committee

Base ISA Ratification Task Group

Privileged ISA Spec Task Group

UNIX-Class Platform Spec Task Group

Formal Specification Task Group

Trusted Execution Env Spec Task Group

B Extension (Bit Manipulation) Task Group

J Extension (Dynam. Translated Lang) Task Group P Extension (Packed-SIMD Inst) Task Group

V Extension (Vector Ops) Task Group Cryptographic Extension Task Group Debug Specification Task Group Fast Interrupts Spec Task Group Memory Model Spec Task Group Processor Trace Spec Task Group

+ Security Committee, HPC Special interest group, soft-core SIG, and Safety Task Group

## **Our Modest RISC-V Project Goal**

# Become the industry-standard ISA for all computing devices

## This is happening!

Far faster, more domains, than anyone predicted Demand at every performance level (low to ludicrous) Demand for all features of all other ISAs ever built!

Using a new community ISA spec development model

## More than 750 RISC-V Members

across 50 Countries

**RISC-V**°

August 2020

| 300 —          | 84 Chip                                                                 | <b>4 Systems</b><br>ODM, OEM<br><b>31 Industry</b><br>Cloud, mobile, HPC, ML, automotive<br><b>49 Research</b><br>Universities, Labs, other alliances |  |  |

|----------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 00 —           | SoC, IP, FPGA                                                           |                                                                                                                                                       |  |  |

| 00             | 61/0                                                                    |                                                                                                                                                       |  |  |

| 00             | Memory, network, storage                                                |                                                                                                                                                       |  |  |

| 100 —<br>300 — | <b>15 Services</b><br>Fab, design services                              |                                                                                                                                                       |  |  |

| 00             | 27 Software                                                             | 450+ Individuals                                                                                                                                      |  |  |

| 0              | Dev tools, firmware, OS                                                 | RISC-V developers and advocates                                                                                                                       |  |  |

| Q.<br>20:      | 3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3<br>15 2015 2016 2016 2016 2016 2017 2017 2017 | Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3<br>2017 2018 2018 2018 2019 2019 2019 2019 2020 2020 2020                                                         |  |  |

So far in 2020, RISC-V membership has grown by more than 50%

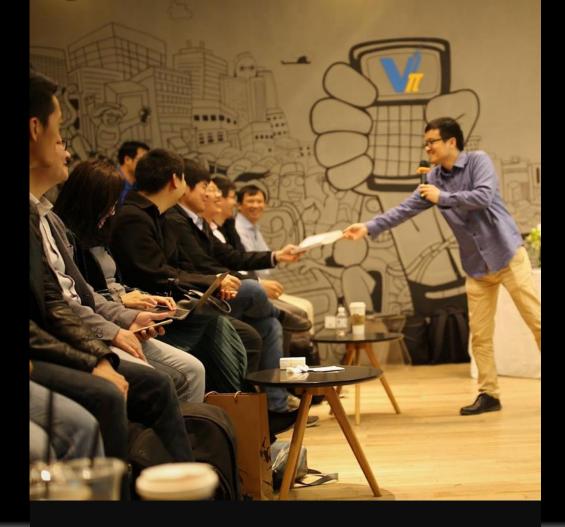

#### CHINA

MORE THAN 200 MEMBERS HAVE JOINED THE CRVA AND CRVIC ASSOCIATIONS AS WELL AS 33 MEMBERS IN THE GLOBAL RISC-V FOUNDATION. ACROSS 2019 WE'VE LED DISCUSSIONS IN 6 CITIES AS WELL AS HOSTED A DAY OF TALKS AT THE WORLD INTERNET CONFERENCE. IN NOVEMBER, WE HOSTED 500 ATTENDEES AT THE CHINA RISC-V FORUM.

#### EUROPE

THE EUROPEAN PROCESSOR INITIATIVE HAS DECLARED RISC-V AS A KEY ARCHITECTURE FOR THE NEXT GENERATION OF HPC PROCESSORS AND SYSTEMS, FOCUSED ON ACCELERATION.

#### INDIA

2014 WITH THE FUNDING OF 6 RISC-V PROCESSORS THROUGH THE SHAKTI PROJECT, RISC-V HAS BEEN WIDELY DECLARED THE NATIONAL ARCHITECTURE OF INDIA.

#### JAPAN

MOMENTUM IS CONTINUING TO GROW IN OUR ENGAGEMENT AND EVENTS WITH A 50% JUMP AT OUR 2019 TOKYO DAY TO 360 REGISTERED ATTENDEES.

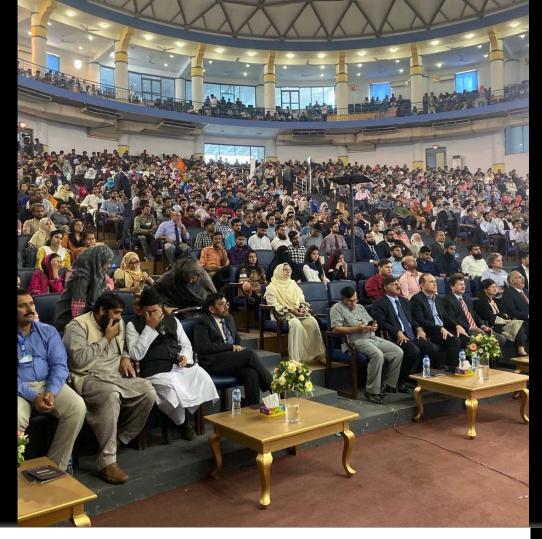

#### PAKISTAN

ON THE ROAD TO DECLARING RISC-V THEIR NATIONAL ARCHITECTURE, TWO OF THE BIGGEST GATHERINGS EVER OF 3000+ IN PAKISTAN FOR TWO SIFIVE TECH SYMPOSIUMS – OCT 2019

#### NORTH AMERICA

NORTH AMERICA. INDUSTRY ADOPTION HAS TAKEN OFF WITH MILLIONS OF CORES SHIPPING FROM NVIDIA, WESTERN DIGITAL, SIFIVE, AND OTHERS.

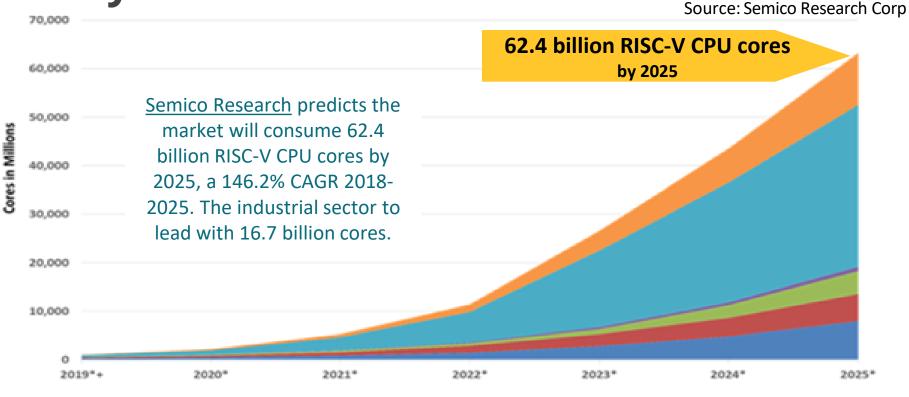

#### Rapid RISC-V growth over next five years led by industrial

- Engineers sometimes "don't see forest for the trees"

- The movement is *not* happening because some benchmark ran 10% faster, or some implementation was 30% lower power

- The movement *is* happening because *new business model* changes everything

- Pick ISA first, then pick vendor or build own core

- Add your own extension without getting permission

- Implementation features/PPA will follow

- Whatever is broken/missing in RISC-V will get fixed

#### **RISC-V in Education**

RISC-V spreading quickly throughout curricula of top schools

## **RISC-V for Space Computing**

- Simple

- Extensible

- Stable

- Secure

## **RISC-V Simplicity**

- Small base, but sufficient to run full C compiler and software stack with good efficiency

- Provides minimal "skeleton" on which to hang additional standard or custom extensions

- Shallow learning curve

- Reduced gate count for small implementations

- Reduced verification cost

- Ease ramp for implementation teams

- Reduce effort for fault-tolerant designs

#### **RV32I** Base Unprivileged Instructions

| imm[31:12]                 |                        |     |       | rd                        | 0110111 | ] LUI          |

|----------------------------|------------------------|-----|-------|---------------------------|---------|----------------|

| imm[31:12]                 |                        |     |       | rd                        | 0010111 | AUIPC          |

| imm[20 10:1 11 19:12]      |                        |     |       | rd                        | 1101111 | JAL            |

| imm[11:0                   | rs1                    | 000 | rd    | 1100111                   | JALR    |                |

| imm[12 10.5]               | rs2                    | rs1 | 000   | imm[4:1 11]               | 1100011 | BEQ            |

| imm[12 10.5]               | rs2                    | rs1 | 001   | imm[4:1 11]               | 1100011 | BNE            |

| imm[12 10:5]               | rs2                    | rs1 | 100   | 1000  imm[4:1 11]         | 1100011 | BLT            |

| imm[12 10.5]               | rs2                    | rs1 | 101   | imm[4:1 11]               | 1100011 | BGE            |

| imm[12 10:5]               | rs2                    | rs1 | 110   | imm[4:1 11]               | 1100011 | BLTU           |

| imm[12 10:5]               | rs2                    | rs1 | 111   | imm[4:1 11]               | 1100011 | BGEU           |

| imm[11:0                   | )]                     | rs1 | 000   | rd                        | 0000011 | LB             |

| imm[11:0                   | <u>ו</u>               | rs1 | 001   | rd                        | 0000011 | LH             |

| imm[11:0                   | <u>ו</u> ו             | rs1 | 010   | rd                        | 0000011 | LW             |

| imm[11:0                   |                        | rs1 | 100   | rd                        | 0000011 | LBU            |

| imm[11:0                   |                        | rs1 | 101   | rd                        | 0000011 | LHU            |

| imm[11:5]                  | rs2                    | rs1 | 000   | imm[4:0]                  | 0100011 | SB             |

| imm[11:5]                  | rs2                    | rs1 | 001   | imm[4:0]                  | 0100011 | SH             |

| $\operatorname{imm}[11:5]$ | rs2                    | rs1 | 010   | $\operatorname{imm}[4:0]$ | 0100011 | SW             |

| imm[11:0                   | )]                     | rs1 | 000   | rd                        | 0010011 | ADDI           |

| imm[11:0                   |                        | rs1 | 010   | rd                        | 0010011 | SLTI           |

| imm[11:0                   | <u>ו</u>               | rs1 | 011   | rd                        | 0010011 | SLTIU          |

| imm[11:0                   | <u>ו</u>               | rs1 | 100   | rd                        | 0010011 | XORI           |

|                            | imm[11:0]              |     | 110   | rd                        | 0010011 | ORI            |

| imm[11:0                   | <u>ו</u> ו             | rs1 | 111   | rd                        | 0010011 | ANDI           |

| 0000000                    | shamt                  | rs1 | 001   | rd                        | 0010011 | SLLI           |

| 000000                     | $\operatorname{shamt}$ | rs1 | 101   | rd                        | 0010011 | SRLI           |

| 0100000                    | $\operatorname{shamt}$ | rs1 | 101   | rd                        | 0010011 | SRAI           |

| 000000                     | rs2                    | rs1 | 000   | rd                        | 0110011 | ADD            |

| 0100000                    | rs2                    | rs1 | 000   | rd                        | 0110011 | SUB            |

| 000000                     | rs2                    | rs1 | 001   | rd                        | 0110011 | SLL            |

| 000000                     | rs2                    | rs1 | 010   | rd                        | 0110011 | SLT            |

| 000000                     | rs2                    | rs1 | 011   | rd                        | 0110011 | SLTU           |

| 000000                     | rs2                    | rs1 | 100   | rd                        | 0110011 | XOR            |

| 000000                     | rs2                    | rs1 | 101   | rd                        | 0110011 | $\mathbf{SRL}$ |

| 0100000                    | rs2                    | rs1 | 101   | rd                        | 0110011 | SRA            |

| 000000                     | rs2                    | rs1 | 110   | rd                        | 0110011 | OR             |

| 000000                     | rs2                    | rs1 | 111   | rd                        | 0110011 | AND            |

| fm pred                    |                        | rs1 | 000   | rd                        | 0001111 | FENCE          |

| 000000000                  | 00000                  | 000 | 00000 | 1110011                   | ECALL   |                |

| 000000000                  | 00000000001            |     | 000   | 00000                     | 1110011 | BREAK          |

28

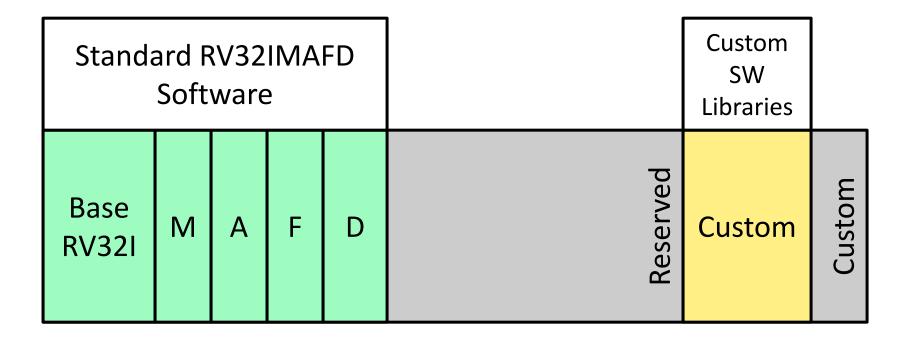

#### **RISC-V Base Plus Standard Extensions**

- Four base integer ISAs

- RV32E, RV32I, RV64I, RV128I

- RV32E is 16-register subset of RV32I

- Only <50 hardware instructions needed for base

- Standard extensions

- M: Integer multiply/divide

- A: Atomic memory operations (AMOs + LR/SC)

- F: Single-precision floating-point

- D: Double-precision floating-point

- G = IMAFD, "General-purpose" ISA

- Q: Quad-precision floating-point

- Above use standard RISC encoding in fixed 32-bit instruction word

- Frozen in 2014, ratified 2019, supported forever after

## **RISC-V Extensibility**

- RISC-V originally designed for research into application-specific processors

- Small base with supported compiler reduces incentive to design new base for each type of core

- No "permission" needed to build your own custom extension

- RISC-V being used in many AI/ML accelerator projects

#### **RISC-V Vector Extension (RVV) Overview**

|                  | v31[0] | v31[1] | v31[VLMAX-1]    |

|------------------|--------|--------|-----------------|

| <u>32 vector</u> |        |        |                 |

| <u>registers</u> |        |        |                 |

|                  | v1[0]  | v1[1]  | <br>v1[VLMAX-1] |

|                  | v0[0]  | v0[1]  | <br>v0[VLMAX-1] |

Vector CSRs

*Vtype sets width of element in each vector register (e.g., 16-bit, 32-bit, ...)*

Vector length CSR sets number of elements active in each instruction

#### vstart

Resumption element after trap

#### vcsr (vxrm/vxsat)

*Fixed-point rounding mode and saturation flag fields in vector CSR*

Maximum vector length (VLMAX) depends on implementation, number of vector registers used, and type of each element.

- Unit-stride, strided, scatter-gather, structure load/store instructions

- Rich set of integer, fixed-point, and floating-point instructions

- Vector-vector, vector-scalar, and vector-immediate instructions

- Multiple vector registers can be combined to form longer vectors to reduce instruction bandwidth or support mixed-precision operations (e.g., 16b\*16b->32b multiply-accumulate)

• Designed for extension with custom datatypes and widths

#### **Some RVV Design Points**

| Name         | Issue<br>Policy | lssue<br>Width | VLEN<br>(bits) | Datapath<br>(bits) | VLEN/Datapath<br>(beats) |

|--------------|-----------------|----------------|----------------|--------------------|--------------------------|

| Smallest     | InO             | 1              | 32             | 32                 | 1                        |

| Simple       | InO             | 1              | 512            | 128                | 4                        |

| InO-Spatial  | InO             | 2              | 128            | 128                | 1                        |

| OoO-Spatial  | 000             | 2-3            | 128            | 128                | 1                        |

| OoO-Temporal | 000             | 2-3            | 512            | 128                | 4                        |

| OoO-Server   | 000             | 3-6            | 2048           | 512                | 4                        |

| OoO-HPC      | 000             | 3-6            | 16384          | 2048               | 8                        |

## **RISC-V Encoding Terminology**

**Standard:** defined by RISC-V **Reserved:** RISC-V might eventually use this space for future standard extensions **Custom:** Space for implementer-specific extensions, never claimed by RISC-V

## **RISC-V Custom Extension Example**

#### **Fragmentation versus Diversity**

#### **Fragmentation:**

Same thing done different ways

#### **Diversity:** Solving different problems

# How is RISC-V Avoiding Fragmentation?

Two powerful forces keep fragmentation at bay:

- Users: No one wants a repeat of vendor lock-in.

- Software: No one, not even nation state, can afford their own software stack. Upstream open-source projects only accept frozen/ratified Foundation standards.

## **RISC-V Stability**

- Designed around small base with modular extensions

- Extensions are frozen and don't change after ratification

- New features via new extensions

- No commercial incentive to force mandatory ISA upgrades

- ISA won't disappear due to merger/acquisition/liquidation

- Original base design will continue to be supported indefinitely

- In 50<sup>th</sup> year of a mission, original RISC-V ISA should still be supported with standard software tools

## **RISC-V Security**

- Original ISA designed with security in mind

- Reduced formal verification effort due to simplicity

- Open ISA design encourages research/inspection

- RISC-V has become focus of secure architecture research community

## **RISC-V for Space Computing**

- Stable, simple, efficient, flexible, secure, open ISA

- Expressly designed to support custom use cases

- Strong and rapidly growing open-source hardware and software ecosystem

- Strong and rapidly growing commercially supported hardware and software ecosystem

- Leading choice for new designs for AI/ML and security